4.3.3 MAC channel

MAC kanál se skládá

z následujících kanálů:

4.3.3.1 Reverse aktivity (RA) kanál

AN používá kanál reverse activity

channel za účelem informování všech AT (ve

svém dosahu) o současných aktivitách na reverse lince.

AT používá tuto informaci při rozhodování

o snížení rychlosti, když je na reverse lince

hustý provoz. Reverse aktivity kanál

přenáší reverse

activity bity.

Při časovém multiplexu jsou reverse

activity bity na forward lince vysílány jednou za

specifikovaný počet časových slotů. Tento

počet časových slotů je specifikován parametrem

RABLength. Protože

každý slot trvá 1,67 ms, jsou reverse activity bity

vysílány rychlostí

1/(RABLength×1,67 ms).

Například, pro RABLength =

2, je rychlost 300 bps (=1/(2×1,67 ms)).

Nutno zdůraznit, že kanály reverse aktivity

channel a reverse power control channel se od sebe liší

v určení příjemců. Zatímco reverse

activity kanál vysílá všem AT, reverse power control

kanál vysílá jednotlivým AT, které

vysílají na reverse lince.

Více informací o časovém

multiplexu různých kanálů na forward lince naleznete

v sekci 4.3.4.

4.3.3.2 Reverse power control (RPC) kanál

AN používá reverse power control

kanál za účelem řízení síly

vysílání AT na reverse lince. Přestože se na

forward lince nepoužívá řízení síly

vysílání, na reverse lince použito je. K tomuto

řízení se používá právě

reverse power control kanál.

Při časovém multiplexu jsou power control

bity na forward lince vysílány jednou za každý

časový slot. Protože každý slot trvá 1,67

ms, jsou tyto bity vysílány rychlostí 600 bps

(=1/1,67 ms). V pozdějších verzích standardu

1xEV-DO byl vytvořen nový MAC kanál DRCLock (viz.

následující sekce), takže reverse power control

kanál nyní sdílí časové sloty

s kanálem DRCLock. Parametr

DRCLockPeriod specifikuje, že

jednou za DRCLockPeriod časový slot je tento slot odebrán

kanálu reverse power control a přidělen kanálu DRCLock.

Takže nyní nejsou reverse power control bity

přenášeny každou 1,67 ms, ale efektivně každou

1,67×DRCLockPeriod/(DRCLockPeriod-1) ms. Například, pro

DRCLockPeriod=8 (slotů), jsou power control bity přenášeny

jednou za 1,67×(8/7) ms nebo tedy jednou za 1,905 ms.

Převrácením této hodnoty získáme

rychlost, s jakou jsou přenášeny power control bity,

což je 525 bps (=1/1,905 ms).

Jak čtenáři jistě ví, kvalita

reverse linky záleží na kvalitě reverse power control

kanálu. Aby se zajistila co nejvyšší kvalita,

musí být zaručeno, že AT správně

přijímá reverse power control kanál. To je ale

obtížné, protože power control bity (zaslané

reverse power control kanálem) nejsou chráněné proti

chybám.

Jeden způsob, jakým 1xEV-DO zajišťuje

kvalitu reverse power control kanálu, je ten, že AT může

různě kombinovat stejné power control bity obdržené

od dvou různých sektorů (na dvou různých reverse

power control kanálech). AN specifikuje, zda AT může nebo

nemůže různě kombinovat reverse power control kanály,

pomocí položky

SofterHandoff ve zprávě

TrafficChannelAssignment. Pokud AN

dovolí kombinování kanálů

v různých sektorech, musí v těchto sektorech

poslat kanálem reverse power control stejné informace.

Více informací o časovém

multiplexu různých kanálů na forward lince naleznete

v sekci 4.3.4.

4.3.3.3 DRCLock kanál

AN používá DRCLock kanál pro

sdělení AT, že AN úspěšně přijal od

AT DRC informace. DRC informace obsahují:

- Datovou

rychlost/délky paketů. Existuje 12 různých

kombinací rychlostí a délek paketů (viz tabulka 4.2).

Každá kombinace je specifikovaná

DRC hodnotou. AT

žádá o rychlost na forward lince zasláním DRC

hodnoty na kanále data rate control channel na reverse

lince.

- Současný

domovský sektor AT. Tento sektor je takový, který AT

zvolí jako nejlepší. AT specifikuje tento

nejlepší sektor použitím

DRCCover. Každý DRCCover je

tří-bitový symbol k

(0 ≤ k ≤ 7), který

pak definuje Walshův kód délky 8. AT pak specifikuje

nejlepší sektor vynásobením kanálu data rate

control channel korespondujícím Walshovým

kódem.

Použitím DRCLock kanálu AN

sdělí AT, že AN úspěšně přijal od AT

DRC informace. Specielně jsou DRCLock kanálem

přenášeny DRCLock bity (indikující

„ano“ nebo „ne“).

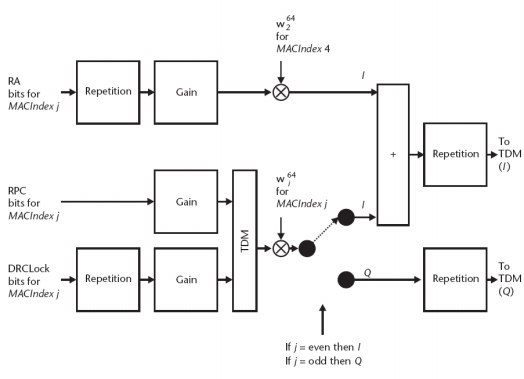

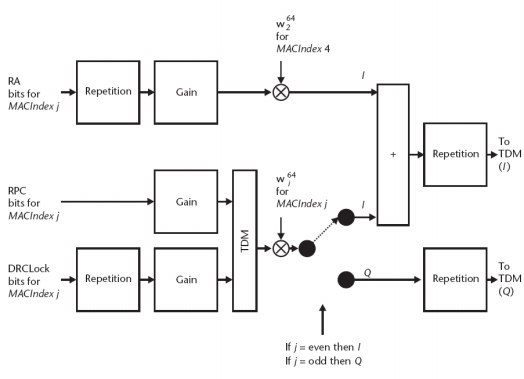

Při časovém multiplexu DRCLock bitů na

forward lince sdílí DRCLock kanál a reverse power control

kanál stejné zdroje MAC kanálů (viz. obrázek

4.5). Parametry DRCLockPeriod a

DRCLockLength specifikují,

jakým způsobem jsou DRCLock bity přenášeny. Jak

bylo zmíněno dříve, DRCLockPeriod specifikuje fakt,

že jeden z DRCLockPeriod slotů je použit pro DRCLock

kanál. DRCLockLength na druhou stranu specifikuje, kolik slotů je

použito pro zopakování jediného DRCLock bitu. Podle

těchto parametrů je tedy jediný DRCLock bit efektivně

přenesen jednou za (DRCLockPeriod × DRCLockLength) slotů.

Protože každý slot trvá 1,66 ms, jsou DRCLock bity

přenášeny 1/(1,66×DRCLockPeriod×DRCLockLength) ms.

Například, pro DRCLockPeriod=8 aDRCLockLength=4, jsou DRCLock bity

přeneseny jednou za 32 slotů rychlostí 18,75 bps.

Obrázek

4.5

Konceptuální blokový

diagram: reverse power control channel, DRCLock channel a reverse activity

channel.Pro zajištění kvality DRCLock kanálu

může AT různě kombinovat stejné DRCLock bity

obdržené od dvou různých sektorů (na dvou

různých DRCLock kanálech). AN specifikuje, zda AT

může nebo nemůže různě kombinovat DRCLock

kanály, pomocí položky

SofterHandoff ve zprávě

TrafficChannelAssignment. Pokud AN

dovolí kombinování kanálů

v různých sektorech, musí v těchto sektorech

poslat kanálem reverse power control stejné informace.

Více informací o časovém

multiplexu různých kanálů na forward lince naleznete

v sekci 4.3.4.

4.3.3.4 Struktura kanálu

Obrázek 4.5 vyobrazuje konceptuální

blokový diagram kanálů reverse power control, DRCLock a

reverse activity. Pokud jde o kanály reverse power control a o

kanál DRCLock, je na bity obou kanálů aplikováno

příslušné zesílení (s výjimkou

DRCLock bitů, které jsou nejdříve zopakovány

faktorem DRCLockLength). Pak jsou tyto dva proudy zkombinovány

s použitím TDM, a na výsledný proud je

aplikován Walshův kód délky 64 definovaný

v MACIndex.

Výsledný proud chipů je přenesen do

I cesty, pokud je MACIndex sudý,

nebo do Q cesty, pokud je MACIndex

lichý. Nakonec obě cesty podstupují repetici, dokud

časový multiplex neskončí s ostatními

kanály na forward lince.

Pokud jde o reverse activity kanál, reverse activity

bity jsou nejdříve zopakovány faktorem

RABLength a je na ně

aplikováno zesílení. Dále je na

výsledný proud aplikován Walshův kód

přiřazený kanálu reverse activity (tj.

w642

korespondující MACIndex 4). Protože reverse activity

kanál používá MACIndex 4, který je sudý,

chipový proud pokračuje po

I cestě.

Připomeňme, že AN používá

kanál reverse activity pro informování všech AT o

všech současných aktivitách na reverse lince.

Důvodem, proč je Walshův kód pro reverse activity

kanál pevný, je, že všechny AT mohou tento kód

kdykoliv použít pro přijetí reverse activity

kanálu a tedy znát současný stav provozu na reverse

lince.

Více informací o časovém

multiplexu různých kanálů na forward lince naleznete

v následující sekci.